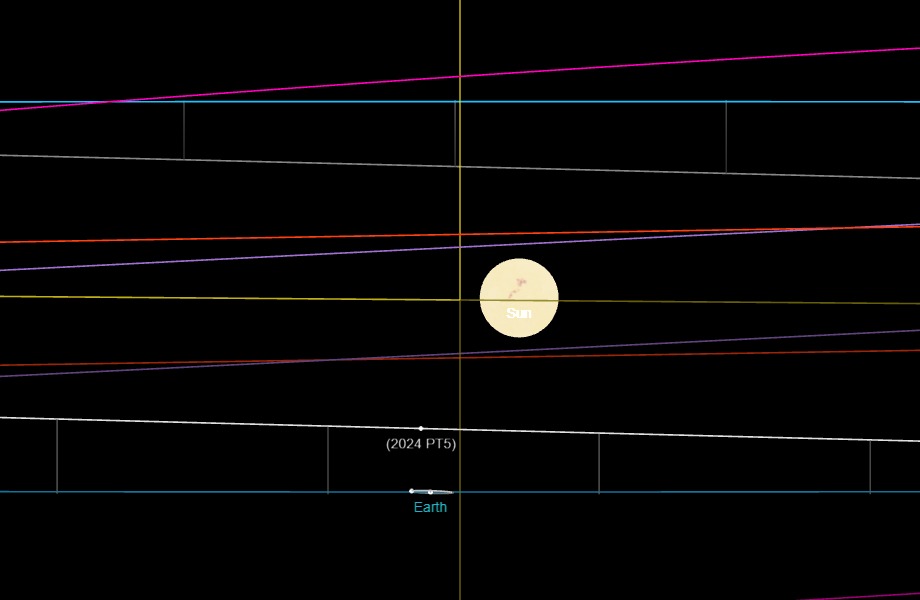

Intel’s Arrow Lake-S Desktop CPU die has been published, giving us a primary take a look at the redesigned P-Core & E-Core configurations. Intel’s Arrow Lake-S Desktop CPU Dies to Show off Greater Design, Lion Cove P-Cores & Skymont E-Core Clusters Built-in In combination It seems like Intel is making a large number of adjustments to the interior design of the next-generation Arrow. Lake CPUs. Consistent with the block diagram shared by way of @Kepler_L2, it seems like the P-Cores and E-Cores shall be strongly configured this time. See extra about ARL-S seems like this? %.twitter.com/WnOr2QR43K — Kepler (@Kepler_L2) January 18, 2024 Beginning with the main points, this symbol is in response to what was once published a couple of 12 months in the past and previous this 12 months, a conceivable translation was once introduced by way of Kepler. adopted by way of Bionic Squash who stated that laptop tiles would seem as a brand new shape. The Arrow Lake CPUs could have 8 P-Cores in response to the Lion Cove structure and 16 E-Cores in response to the Skymont E-Core structure. This will likely lead to as much as 24 cores and 24 threads because the CPUs are stated not to give a boost to hyper-threading.

Intel Lion Cove P-Cores for Lunar Lake CPUs have 2.5 MB L2 core however Arrow Lake CPUs could have 3.0 MB L2 cache core and three MB L3 cache for a complete of 24 MB L3 that shall be totally allotted whilst Skymont E-Cores could have 4 MB of L2 cache in keeping with team and each and every team shall be getting 3 MB of L3 cache. Arrow Lake P-Core Cache (Lion Cove): 3 MB L2 / 3 MB L3 Arrow Lake E-Core Cache (Skymont): 4 MB L2 / 3 MB L3 Raptor Lake P-Core Cache (Raptor Cove): 2 MB L2 / 3 MB L3 Raptor Lake E-Core Cache (Gracemont): 4 MB L2 / 3 MB L3 The fascinating factor is that each and every pair of Lion Cove P-Cores could have an E-Core cluster stacked within the heart and might not be there. separated by way of P-Cores as up to now designed. This new function can assist toughen chip connectivity which is able to assist the Thread Supervisor to higher make a selection which cores to make use of for the process and in addition assist with Latencies at the attached ring buses. The commute time can also be decreased because the E-Cores are most often positioned on the very finish of the die which means that that the primary P-Core connects to the primary E-Core by way of touring between all cores however having an E.-Core cluster subsequent to each and every P-Core can fixing most of the conversation issues skilled by way of the Alder Lake & Raptor Lake chips. Intel has already showed that the Lion Cove P-Core to Lunar Lake and Arrow Lake CPUs are other in lots of respects.

For Lunar Lake, Thread Director begins at E-Cores however for upper choices, it begins at P-Cores giving OEMs the versatility to modify the time table consistent with their wishes. Thread Course offers the theory of the place to position the paintings, the overall determination rests with the OS. This shall be a fascinating determination made by way of Intel for its subsequent era Arrow Lake CPUs. The construct will increase to desktop and cellular and can debut on desktop by way of October so keep tuned for more info within the coming months. Article Supply: TechPowerUp